Digital Pll Loop Filter Design Phase Locked Loop Tutorial | PLL Basics - YouTube fpga - Loop Filter in all digital PLL cutoff? - Electrical Engineering Stack Exchange What is Phase Lock Loop (PLL)? How Phase Lock Loop Works ? PLL Explained - YouTube Phase-Locked Loop (PLL) Fundamentals | Analog Devices JLPEA | Free Full-Text | Memristor-Based Loop Filter Design for Phase Locked Loop | HTML Digital PLL 7 Time to digital TDC converts input phase error to a digital word Digital loop filter provides PI control to allow for a

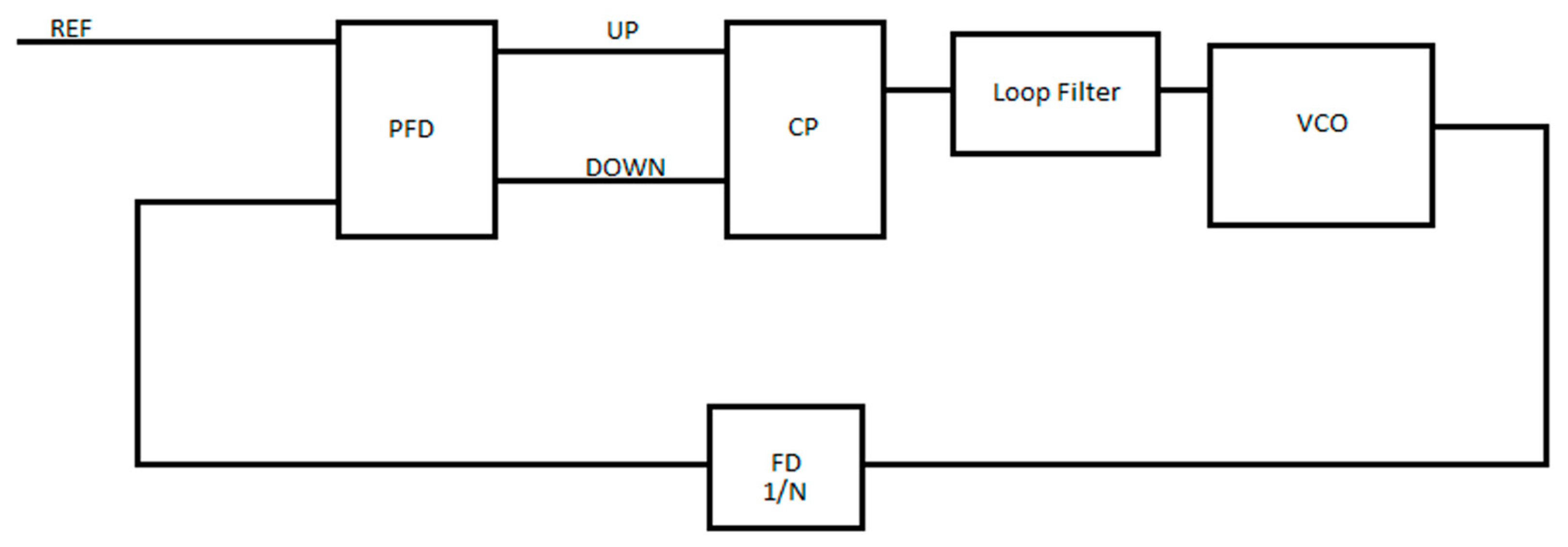

Digital phase locked loops are typically smaller than analog PLLs due to their digital phase detector and loop filter However both analog PLLs and digital Four design methodologies for loop filters for a class of digital phase locked loops DPLLs are presented The first design maps an optimum analog filter

JLPEA | Free Full-Text | Memristor-Based Loop Filter Design for Phase Locked Loop | HTML Digital PLL Frequency Synthesizers: what they are, how they work - YouTube Phase lock loop (PLL) bandwidth design - Part 1 | TI.com Video Consider the Source Part 1: What is a Phase Locked Loop? Electronics | Free Full-Text | Design and Emulation of All-Digital Phase-Locked Loop on FPGA | HTML PLL Phase Locked Loop on LTSpice - YouTube JLPEA | Free Full-Text | Memristor-Based Loop Filter Design for Phase Locked Loop | HTML 1.5 GHz PLL Frequency Synthesizer Phase Locked Loop (PLL) in a Software Defined Radio (SDR) - Wireless Pi

Digital Pll Loop Filter Design

Digital Pll Loop Filter Design

Digital Pll Loop Filter Design

https://i.ytimg.com/vi/A9qt0JYdvFU/maxresdefault.jpg

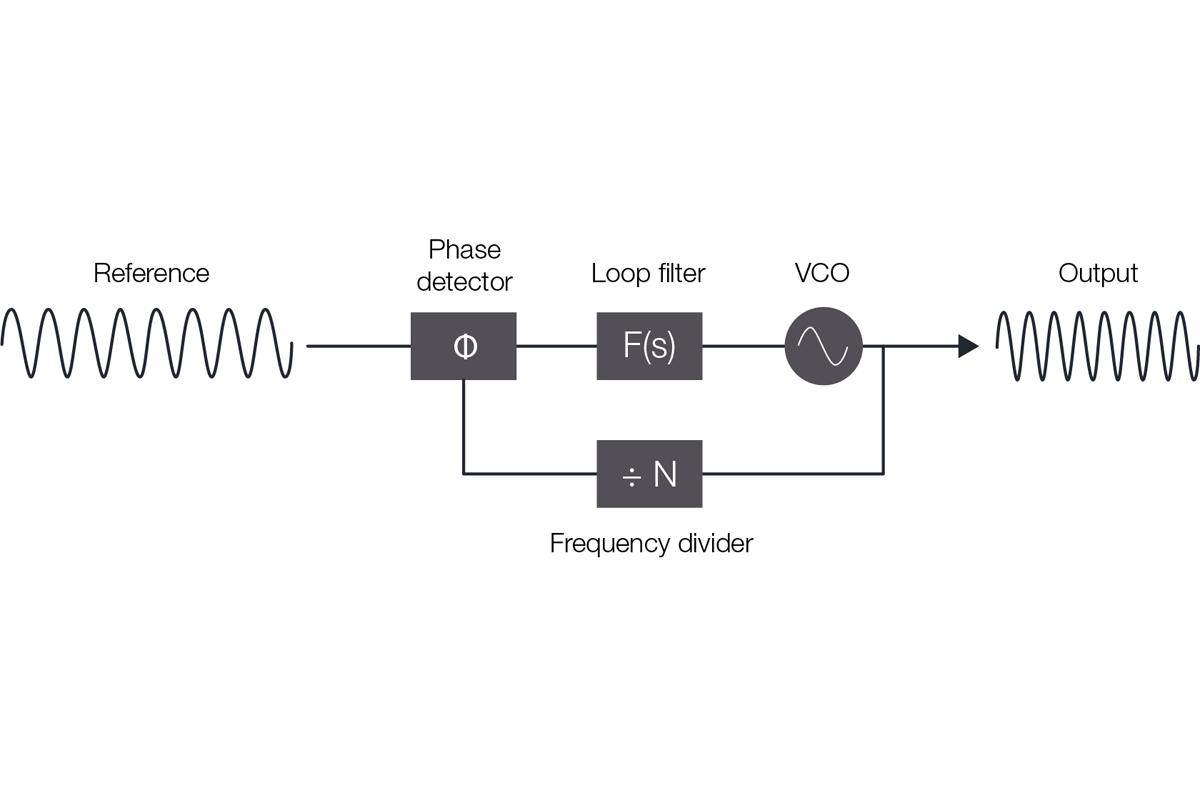

For phase locked loop circuits the bandwidth of the low pass filter has a direct influence on the settling time of the system The low pass filter is the final

Templates are pre-designed files or files that can be used for numerous purposes. They can conserve effort and time by providing a ready-made format and layout for producing various type of content. Templates can be utilized for personal or expert jobs, such as resumes, invitations, leaflets, newsletters, reports, discussions, and more.

Digital Pll Loop Filter Design

Sensors | Free Full-Text | Analysis and Design of Integrated Blocks for a 6.25 GHz Spacefibre PLL | HTML

Digital PLL Frequency Synthesizers: what they are, how they work - YouTube

Phase lock loop (PLL) bandwidth design - Part 1 | TI.com Video

Consider the Source Part 1: What is a Phase Locked Loop?

PLL Phase Locked Loop on LTSpice - YouTube

JLPEA | Free Full-Text | Memristor-Based Loop Filter Design for Phase Locked Loop | HTML

Abstract In this brief a systematic design procedure for a second order all digital phase locked loop PLL is proposed The design procedure is based on

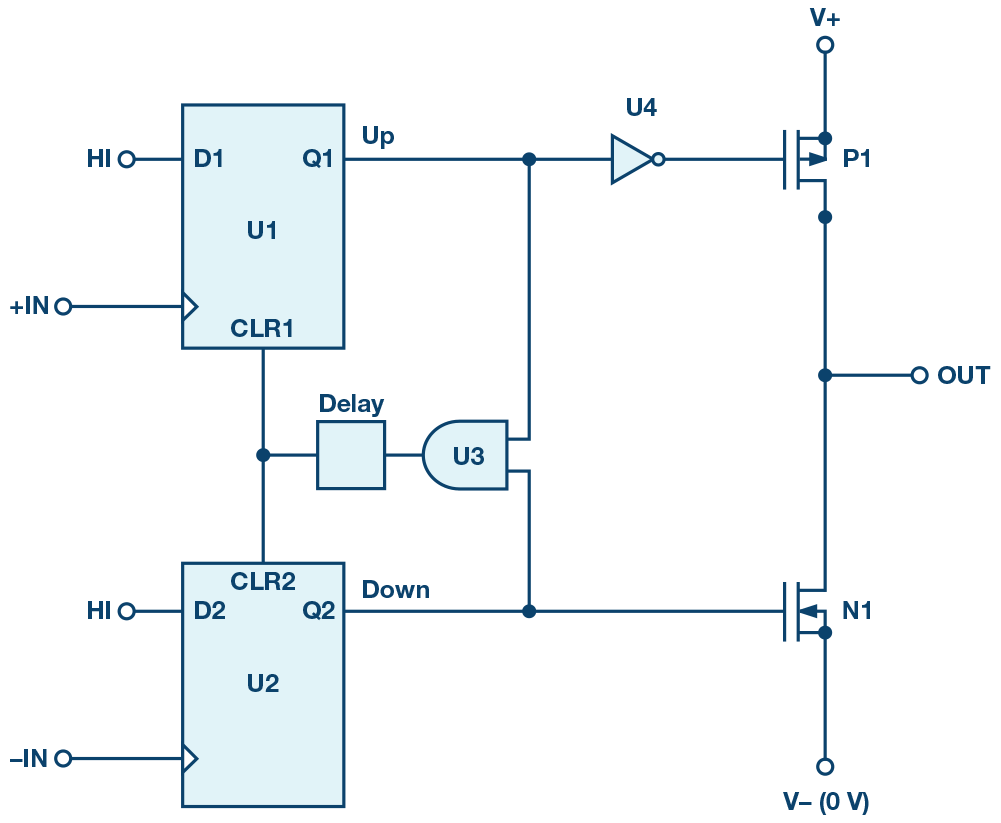

Are designed and layed out in a 0 5um CMOS process One is has a 30MHz starved inverter VCO a programmable divider and a phase frequency detector

This thesis presents the design of an All Digital Phase Locked Loop ADPLL using a Table 2 3 Summary of the Transfer Functions of the Loop Filters

Abstract Modern digital telecommunication and audio systems include a Digital Phase Locked Loop D PLL in a form of a device or an algorithm

An analog loop filter is designed to achieve a specified loop bandwidth and phase margin then the circuit values and sample interval are translated to digital

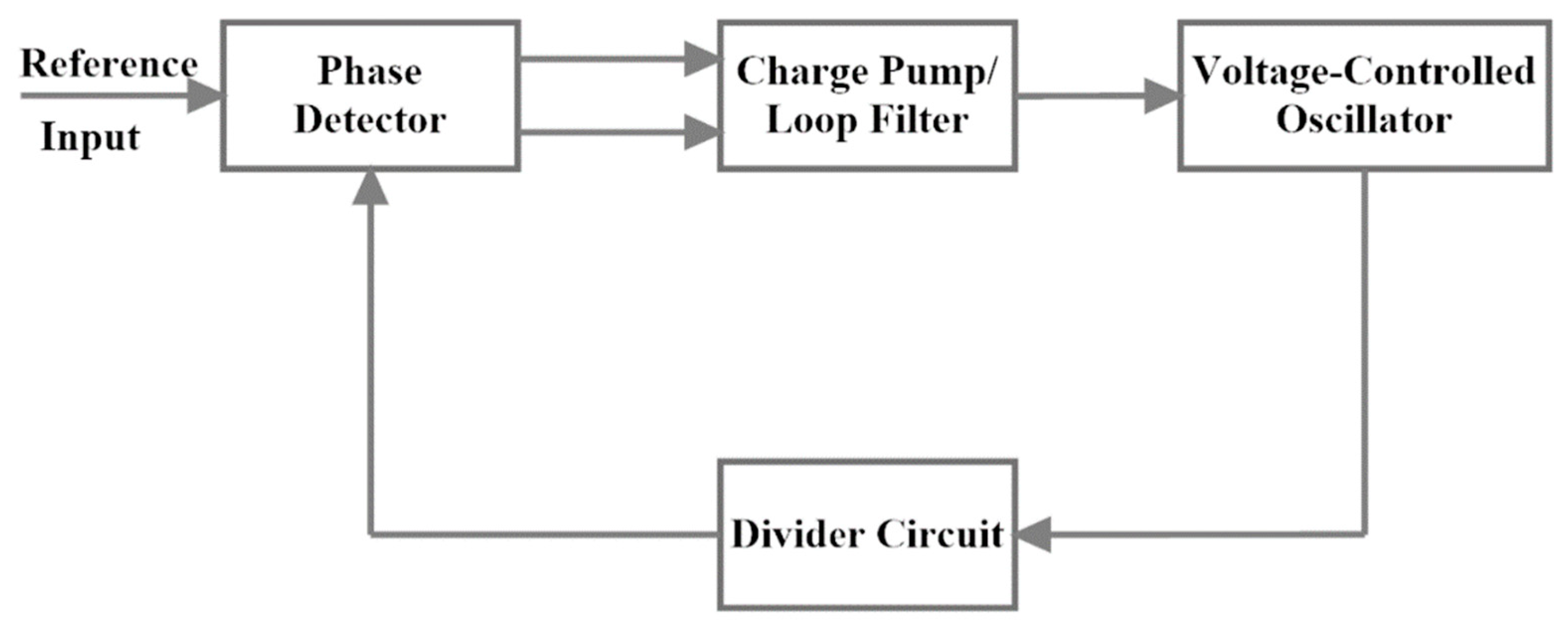

a time b time Figure 19 9 Average output voltage of phase detector during acquisition To summarize the design criteria of the VCO with the XOR PD we The loop includes a phase detector to compute phase error and a loop filter to set loop dynamic performance The output of the loop filter

The main advantage of the PLL with a digital loop filter is that it The main challenge in DPLL design is to obtain a wide bandwidth PLL