Example Design 3 2 English Xilinx Building the Example Design - 3.1 English Step 4: Launching the Vivado IDE - 2020.2 English Step 1: Opening the Example Project - 2020.2 English Example Design Tab - 3.1 English Step 1: Creating a New Project - 2020.2 English Zynq UltraScale RFSoC RF Data Converter Gen 1 2 3 DFE LogiCORE IP Product Guide PG269 Document ID PG269 Release Date 2022 10 21 Version 2 6 English

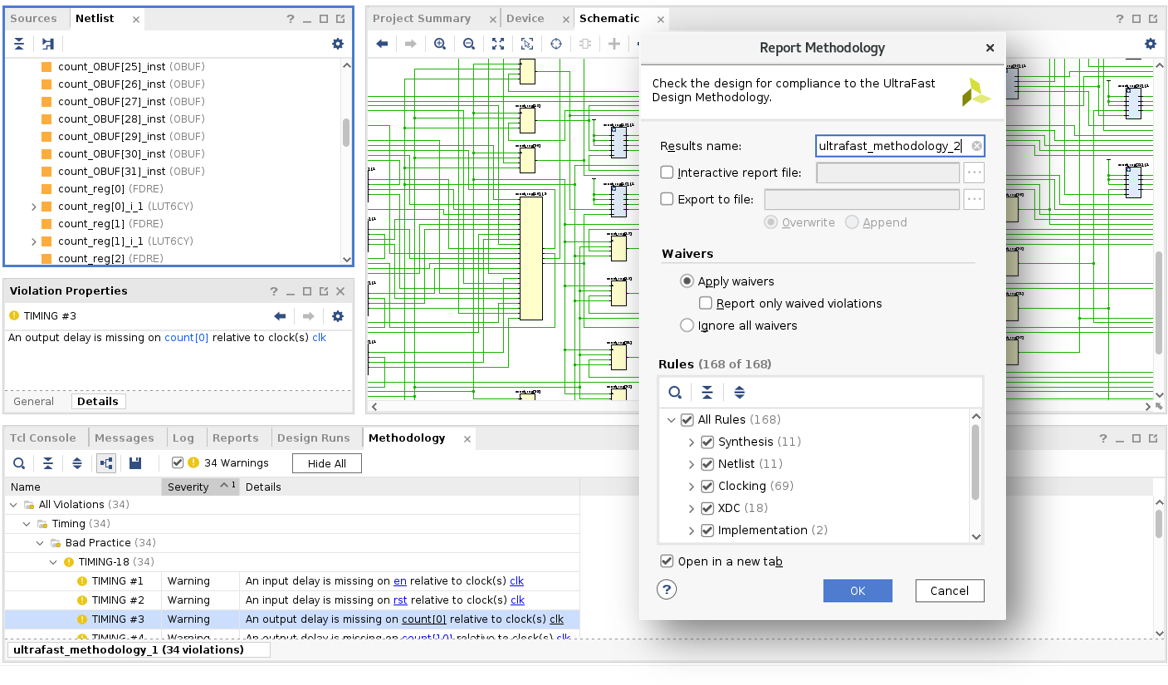

Open the Vivado Design Suite and create a new project In the pop up window press Next until you get to the page to select the Xilinx part or board for the This chapter contains information about the example design provided in the Vivado Design Suite The top module instantiates all components of the core and

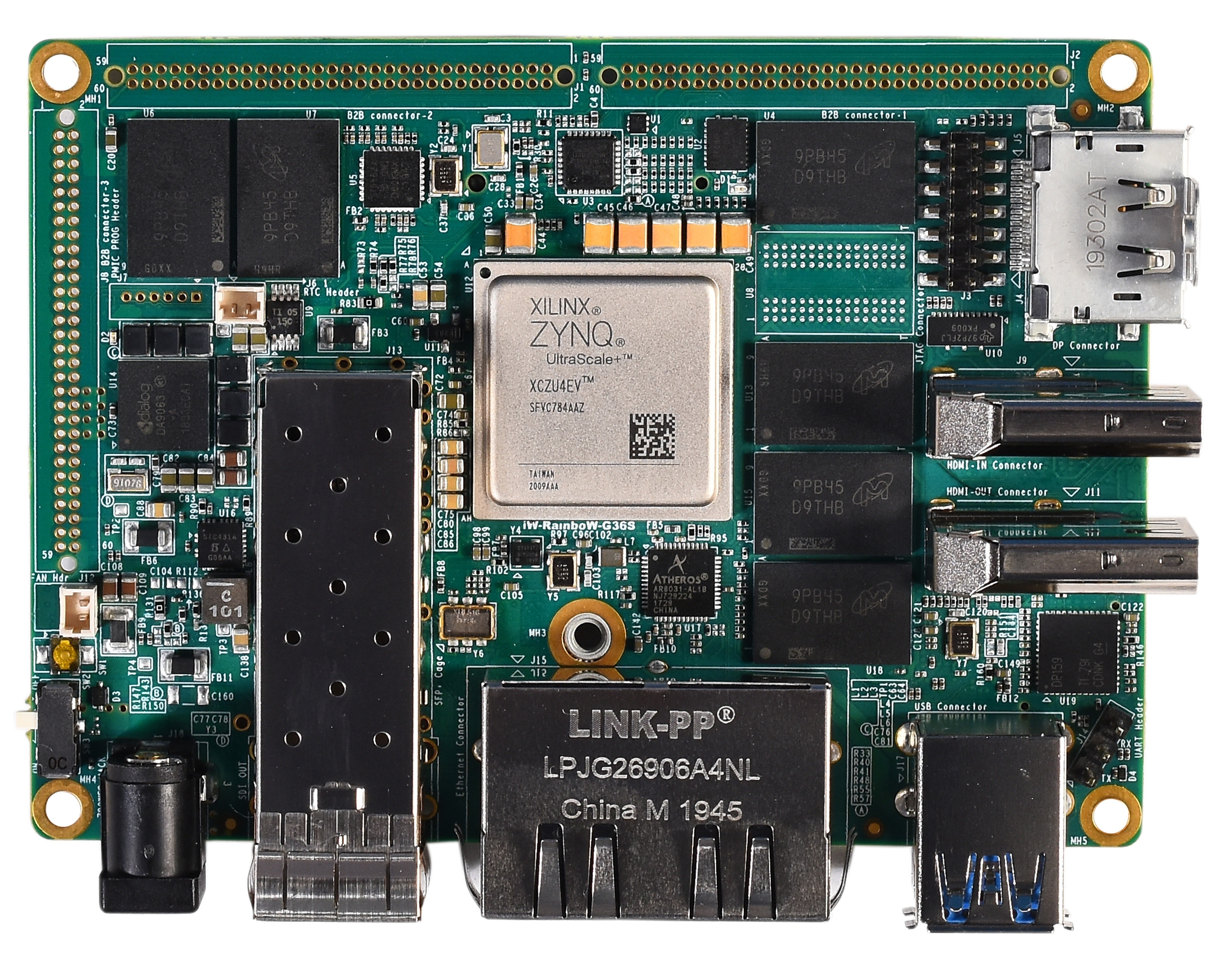

Step 1: Creating a New Project - 2020.2 English Advanced ZU5/4/3/2 Zynq Ultrascale+ SBC Design Flows - 2022.2 English Implementation AXI Memory Mapped Interfaces & Hardware Debugging in Vivado (Lesson 5) - YouTube Step 1: Opening the Project - 2021.2 English High Level Design Verification Step 2: Create a Vivado Project using System Generator IP - 2020.2 English

Example Design 3 2 English Xilinx

Example Design 3 2 English Xilinx

x-raw-image:///6f26c7922db0e8b3e715c0465d76c7b7ac35a43b08d164a338297de5e51a1d06

2 Select the FPGA part that you wish to use 3 Using the Vivado IP catalog select the JESD204C IP core

Templates are pre-designed files or files that can be used for numerous purposes. They can conserve effort and time by offering a ready-made format and layout for developing various kinds of material. Templates can be utilized for individual or professional tasks, such as resumes, invitations, flyers, newsletters, reports, presentations, and more.

Example Design 3 2 English Xilinx

Step 3: Running Behavioral Simulation - 2020.2 English

Advanced ZU5/4/3/2 Zynq Ultrascale+ SBC

Design Flows - 2022.2 English

Implementation

Step 1: Opening the Project - 2021.2 English

High Level Design

Example Design 2 3 English MIPI DSI Transmitter Subsystem Product Guide PG238 Document ID PG238 Release Date 2022 10 19

The following table shows the example designs available for the TX and RX DisplayPort 1 4 subsystems FB Pass through with HDCP1 3 and HDCP2 2 2 3 QPLL

This chapter contains step by step instructions for generating an Application Example Design from the DisplayPort 1 4 TX Subsystem by using the Vivado Design

Open the Vivado Design Suite and click Create Project In the New Project window enter a Project name Project location and click Next up to the

Vivado Design Suite Tutorial Logic Simulation UG937 You will now generate an AXI VIP example design Create a project with the name mySystemVerilog by

This section contains information about the provided test bench in the Vivado Design Suite Figure 5 2 AXI VDMA Example Design Test Bench Labs 1 through 4 include A simple control state machine Three sine wave generators using AXI4 Stream interface native DDS Compiler Common push buttons

The DFX Controller IP is created but the design is not yet compiled In order to create the PROM image with all the necessary full and partial images